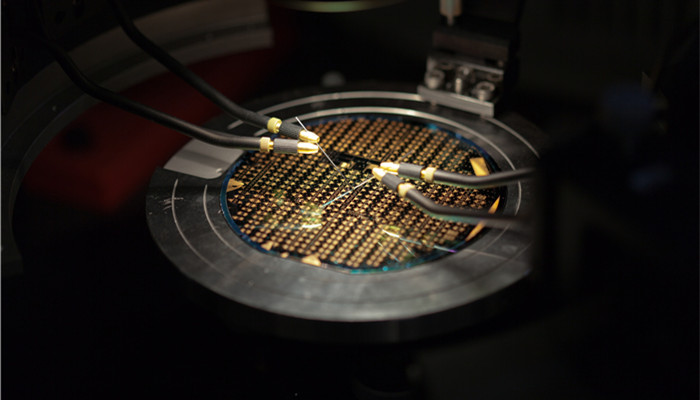

ĪĪĪĪSTCOŻ¼ŽĄĮy╣ż╦ćģf═¼ā×╗»Ż¼š¹║ŽąŠŲ¼įOėŗĪóųŲįņ╣ż╦ćĪóĘŌčb╝╝ągĪóŽĄĮy╝▄śŗĪó▓─┴Žķ_░lĪóįOéõķ_░lĪó▄ø╝■ā×╗»Ą╚ČÓéĆŁh╣ØŻ¼īŹ¼FąŠŲ¼ųŲįņ╚½┴„│╠ģf═¼ā×╗»Ż¼═╗ŲŲé„Įyå╬ę╗Łh╣Øā×╗»Ą─ŠųŽ▐ąįŻ¼─┐Ą─╩Ūį┌ŽĄĮyš¹¾wīė├µ╔ŽīŹ¼FąŠŲ¼Ą─ąį─▄Īó╣”║─Īó├µĘeĪó│╔▒ŠŻ©PPACŻ®Ą─ūŅā×ŲĮ║ŌĪŻ

ĪĪĪĪĖ∙ō■ą┬╦╝Įń«aśI蹊┐ųąą─░l▓╝Ą─

ĪČ2025-2029─Ļųąć°STCOŻ©ŽĄĮy╣ż╦ćģf═¼ā×╗»Ż®╩ął÷┐╔ąąąį蹊┐ł¾ĖµĪĘ’@╩ŠŻ¼į┌─”Ā¢Č©┬╔Ž┬Ż¼Š¦¾w╣▄│▀┤ń▓╗öÓ┐sąĪŻ¼å╬╬╗├µĘe╣ĶŲ¼╔ŽŠ¦¾w╣▄╝»│╔öĄ┴┐│ų└mĘŁ▒ČŻ¼╩╣Ą├ąŠŲ¼ėŗ╦Ń╦┘Č╚Īó╠Ä└Ē─▄┴”ļSų«╠ß╔²ĪŻį┌╚╦╣żųŪ─▄Ģr┤·▒│Š░Ž┬Ż¼╦Ń┴”ąĶŪ¾į÷ķL╦┘Č╚╝ė┐ņŻ¼═¼ĢrŻ¼ąŠŲ¼Ą─╣”║─Īó¾wĘeĪó│╔▒ŠĄ╚ę¬Ū¾ę▓į┌╠ßĖ▀ĪŻ«öŪ░Ż¼Š¦¾w╣▄│▀┤ńęčĮėĮ³╬’└ĒśOŽ▐Ż¼Š¦¾w╣▄├▄Č╚ļyęį├„’@╠ß╔²Ż¼ę└┐┐į÷╝ėŠ¦¾w╣▄öĄ┴┐Ą─ĘĮ╩Į¤oĘ©ØMūŃąŠŲ¼ąį─▄▀Mę╗▓Į╠ßĖ▀Ą─ę¬Ū¾ĪŻę“┤╦Ż¼STCOĖ┼─Ņ▒╗╠ß│÷ĪŻ

ĪĪĪĪSTCOį┌DTCOĄ─╗∙ĄA╔Žčė╔ņ░lš╣Č°üĒĪŻDTCOŻ¼įOėŗ╣ż╦ćģf═¼ā×╗»Ż¼īóICįOėŗĪóEDA╣żŠ▀Īó░ļī¦¾wįOéõĪ󊦳A┤·╣żĄ╚Łh╣Øģf═¼ā×╗»ĪŻļSų°ąŠŲ¼╣”─▄╝»│╔Č╚╚šęµ╠ßĖ▀Ż¼ŲõįOėŗĪó╔·«aÅ═ļsąį╚šęµį÷┤¾Ż¼āHę└┐┐å╬ę╗Łh╣Ø╗“▓┐ĘųŁh╣Øā×╗»Ż¼ęč¤oĘ©ØMūŃPPACŲĮ║ŌąĶŪ¾ĪŻSTCOį┌DTCOĄ─╗∙ĄA╔Ž▀Mę╗▓ĮöU┤¾ģf═¼ā×╗»ĘČć·Ż¼į┌ŽĄĮyīė├µ╔ŽīŹ¼FąŠŲ¼ųŲįņ╚½┴„│╠ģf═¼ā×╗»Ż¼┐╔ęį═Ļ│╔DTCO¤oĘ©═Ļ│╔Ą─╣żū„Ż¼└²╚ń▓╗ę└┐┐Š¦¾w╣▄│▀┤ń┐sąĪüĒ£p╔┘SRAMŻ©ņoæBļSÖC┤µā”Ų„Ż®┤µā”å╬į¬├µĘeĪŻ

ĪĪĪĪSTCO┐╔ęįæ¬ė├į┌┤µ╦Ńę╗¾wąŠŲ¼įOėŗĪóųŲįņŅIė“ĪŻ┤µ╦Ńę╗¾wąŠŲ¼╩Ūę╗ĘNą┬ą═ėŗ╦Ń╝▄śŗŻ¼īó┤µā”å╬į¬┼cėŗ╦Ńå╬į¬╝»│╔ė┌ę╗¾wŻ¼─┐Ą─╩Ū╠ß╔²öĄō■╠Ä└Ēą¦┬╩ĪŻį┌╚╦╣żųŪ─▄▒│Š░Ž┬Ż¼┐╔æ¬ė├ĘČć·ÅVĘ║Ą─┤µ╦Ńę╗¾wAIąŠŲ¼ķ_░l┼cæ¬ė├╩▄ĄĮųžęĢŻ¼ŽÓĻP┐ŲčąÖCśŗĪó▓╝ŠųŲ¾śIöĄ┴┐▓╗öÓį÷ČÓĪŻSTCO▓╔ė├3DĘŌčb╗“š▀2.5DĘŌčb╝╝ągŻ¼┐╔ęįīŹ¼F┤µ╦Ńę╗¾w╝▄śŗŻ¼═ŲäėąŠŲ¼╦Ń┴”╠ß╔²ĪŻ

ĪĪĪĪ2022─ĻŻ¼▒╚└¹Ģr╬óļŖūė蹊┐ųąą─Ż©IMECŻ®į┌š╣╩Š░ļī¦¾wŲ„╝■═╗ŲŲ╬óą═╗»śOŽ▐┬ĘŠĆĢrŻ¼ī”STCO╝╝ąg▀Mš╣ųžęĢŻ¼Ųõ░lš╣ųžą─╩Ū═©▀^╣ż╦ć▀M▓ĮīŹ¼F┤µ╦Ńę╗¾w╝▄śŗĪŻ2024─ĻŻ¼┼_ĘeļŖ┐éĮø└Ēč▌ųvĢr▒Ē╩ŠŻ¼╬┤üĒīó═©▀^Š¦¾w╣▄├▄Č╚╠ßĖ▀ĪóDTCO/STCOĪó2.5D/3DĘŌčb┼c╣ĶČč»B╚²ĘN╝╝ągüĒīŹ¼F░ļī¦¾wŲ„╝■╦Ń┴”┼c─▄ą¦╠ß╔²ĪŻ

ĪĪĪĪą┬╦╝Įń

ąąśIĘų╬÷╚╦╩┐▒Ē╩ŠŻ¼2024─Ļ8į┬Ż¼╬ęć°╣żą┼▓┐░l▓╝ć°╝ęųž³cčą░lėŗäØ“╬ó╝{ļŖūė╝╝ąg”ųž³cīŻĒŚ2024─ĻČ╚ĒŚ─┐╔Ļł¾ųĖ─ŽŻ¼╠ß│÷├µŽ“AIąŠŲ¼Ė▀╦Ń┴”ĪóĖ▀ĦīÆąĶŪ¾Ż¼╗∙ė┌2.5DŽ╚▀MĘŌčb╝╝ągŻ¼ķ_š╣ŽĄĮy-╣ż╦ćģf═¼įOėŗā×╗»Ż©STCOŻ®ĘĮʩ蹊┐ĪŻÅ─ć°ļHŅIŽ╚ÖCśŗĪóŲ¾śIęį╝░╬ęć°š■Ė«æBČ╚üĒ┐┤Ż¼STCO╩Ū╬┤üĒąŠŲ¼╝╝ąg░lš╣┌ģä▌Ż¼ąąśIŪ░Š░śO×ķÅVķ¤ĪŻ